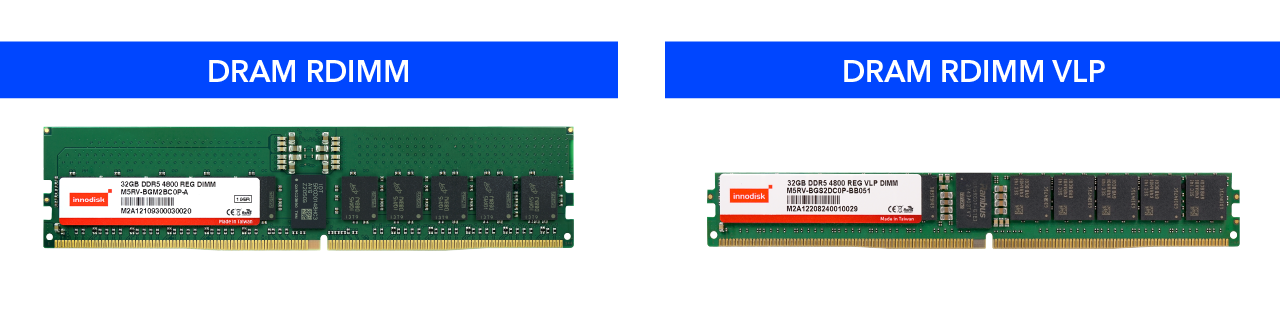

深度了解 DDR5 RDIMM VLP 的節省空間優勢

隨著高效能運算(HPC)需求日益增長,以及數據資料與產業應用的日趨複雜,在有限空間下的終端應用場域,也逐漸受到重視。在這樣的背景下,DDR5 RDIMM VLP 記憶體模組便扮演了關鍵角色。本文將帶您深入了解 DDR5 RDIMM VLP,從技術上的挑戰與突破,到它的優勢與效益。

DDR5 RDIMM VLP 的常見應用場景

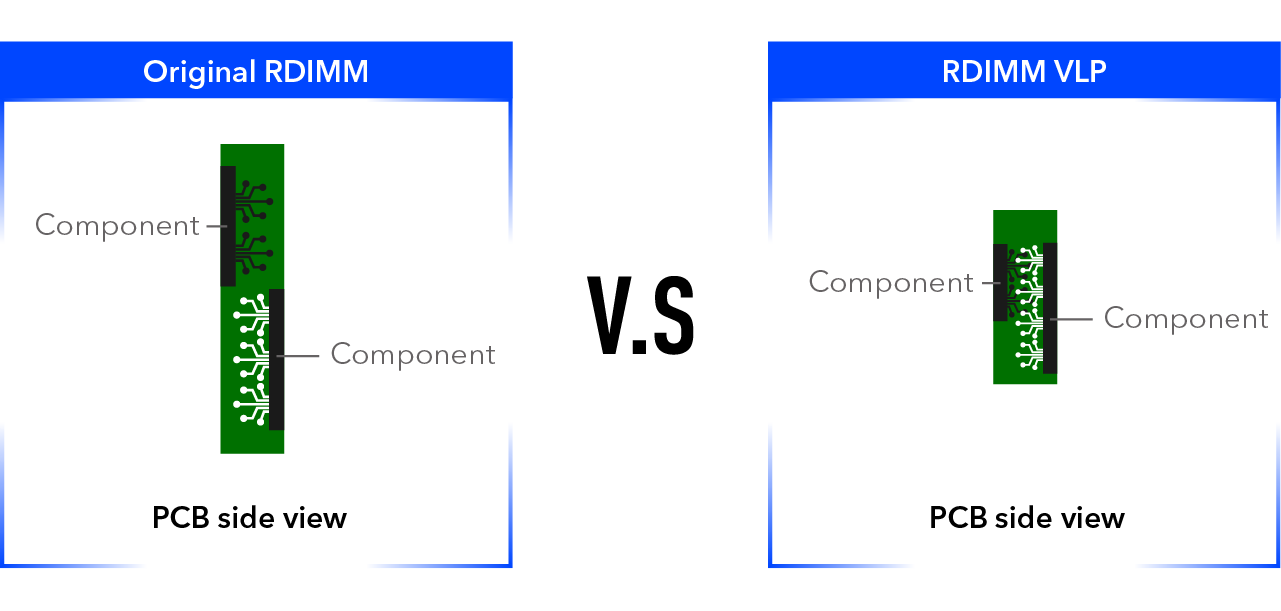

DDR5 RDIMM VLP 記憶體模組廣泛應用於各種運算環境中,特別是在系統空間有限的伺服器架構中,尤能展現其優勢。這類模組透過縮減電路板(PCB)的實際高度,有效減少體積,同時保有效能與穩定性。不論是部署在緊湊型刀鋒伺服器(blade servers),還是其他空間受限的系統設備中,DDR5 RDIMM VLP 都能提升伺服器的密度與運作效率。

DDR5 RDIMM VLP 的優勢

DDR5 RDIMM VLP 模組具備多項關鍵優勢,使其在空間受限的伺服器架設環境中,成為不可或缺的記憶體解決方案。

1. 更小的實體體積

VLP 模組具備更小的規格尺寸,讓伺服器能夠配置更高密度的記憶體,進一步在有限的空間內擴充容量,同時不影響整體效能與穩定性。

2. 優異的散熱效能與設計彈性

DDR5 RDIMM VLP 採用精巧設計,使伺服器內部配置更具彈性。由於記憶體模組時常緊鄰 CPU、GPU 等容易產生熱能的元件,此時, DDR5 RDIMM VLP 的小尺寸設計,便能促進氣流循環,有效提升散熱效率、降低系統溫度,進而提升系統穩定性與長時間運作的可靠性。此外,節省下的空間更能創造系統設計的靈活性,協助企業最佳化伺服器部署,實現高效率與可擴充性兼備的解決方案。

3. 降低系統整體功耗

DDR5 RDIMM VLP 不僅強化了散熱效能,也進一步降低整體系統功耗。藉由提升被動散熱的效率,能夠減少風扇與其他主動散熱機制的依賴,進而降低電源利用,創造更具永續性與可靠性的伺服器架構。

DDR5 RDIMM VLP 模組可說是現代化伺服器架構的關鍵零組件,讓高密度記憶體能夠無縫整合至空間有限的資料中心,優化系統部署效率與擴充性。

產品開發的技術挑戰

為全球領先的工控記憶體模組品牌,宜鼎在開發 DDR5 RDIMM VLP 模組的過程中,仍面臨各式技術挑戰。其中一大關鍵在於如何確保新一代 DDR5 記憶體元件能夠與各式各樣的主機板有效相容。此外,在縮小模組尺寸的同時,仍需符合業界對於效能與穩定性的嚴格標準,也是技術上的一大考驗。然而,透過嚴謹的測試流程與創新的設計思維,我們成功克服了這些挑戰,並推出具備高效能與穩定性的 DDR5 RDIMM VLP 記憶體模組。

技術創新與突破

為了解決上述技術難題,我們採取多項策略,確保模組能兼顧最佳效能與可靠性。在整體開發過程中,我們持續進行測試與驗證,特別針對 DDR5 記憶體元件的相容性,規劃出三大核心驗證項目:

- PMIC 電源完整性測試(Power Integrity, PI)

- SPD Hub 訊號完整性測試(Signal Integrity, SI)

- Rank Margin Test(RMT)測試

透過細緻的分析每個零組件的穩定性驗證結果,我們得以設計並開發出最高標準的記憶體模組。

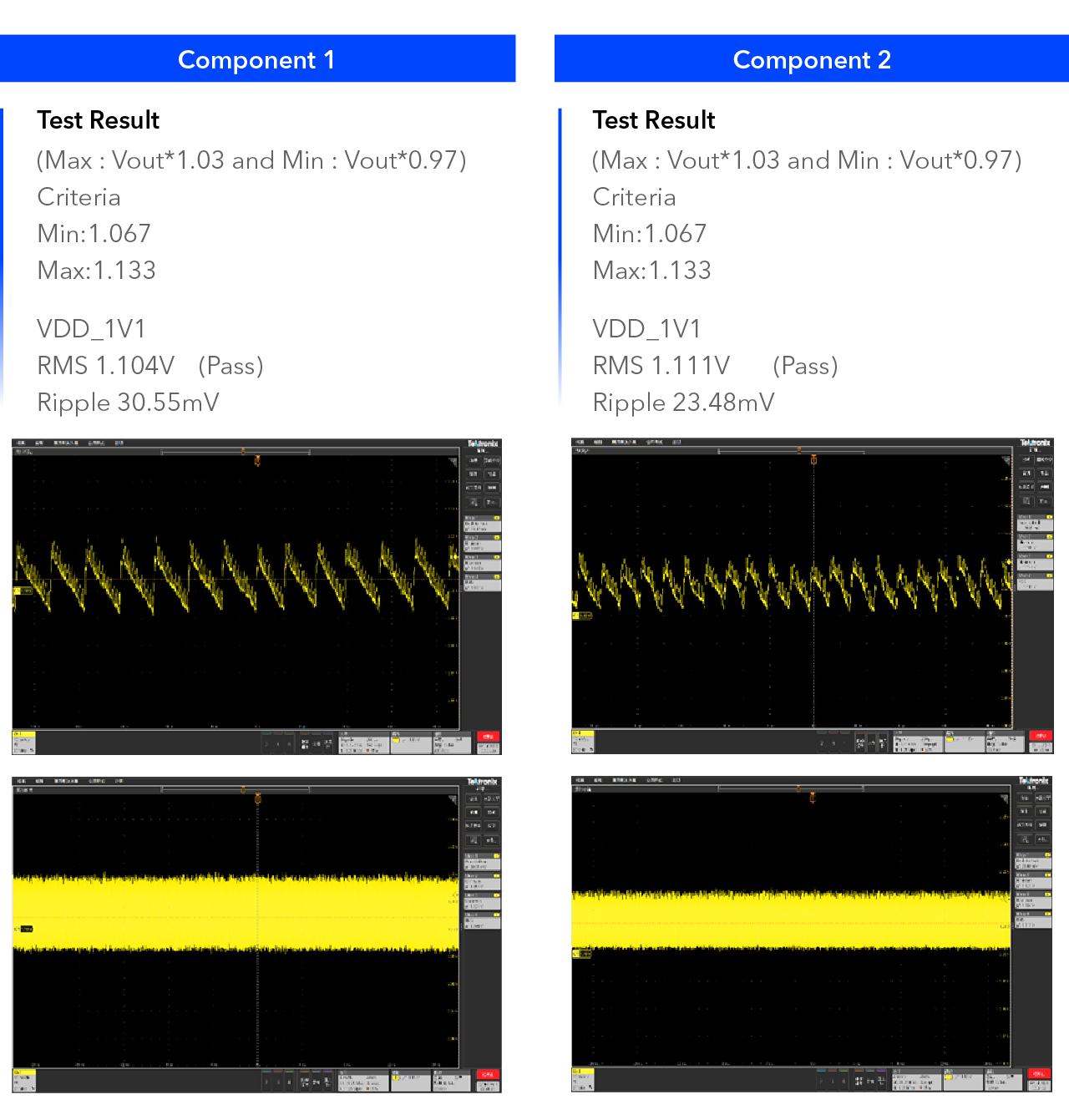

PMIC 電源完整性(PI)測試:確保訊號穩定性

PMIC(電源管理積體電路)在 DRAM 模組中扮演電力分配與穩定電壓的角色。當電壓由 12V 降至 1.1V,其過程中產生的電壓波動與雜訊,可能影響 DRAM 模組的效能與穩定性。即使這些元件符合 JEDEC 標準,不同主機板與零組件搭配下的 PMIC 表現與抗雜訊能力,仍可能有所不同。

為了驗證供電穩定性,我們針對來自多家供應商的 PMIC 進行電源完整性(PI)測試。穩定的電源供應,對於訊號的傳輸與接收至關重要。例如,在下圖中可見,元件 A 的電源紋波雜訊明顯高於元件 B。過高的紋波雜訊(Ripple Noise)與電壓振幅,會導致電源供應不穩定,進而影響整體記憶體模組效能。

因此,較低的紋波雜訊代表更佳的訊號穩定性,使得元件 B 成為在高效能環境下更可靠的選擇,有助於維持 DRAM 模組的穩定運作。

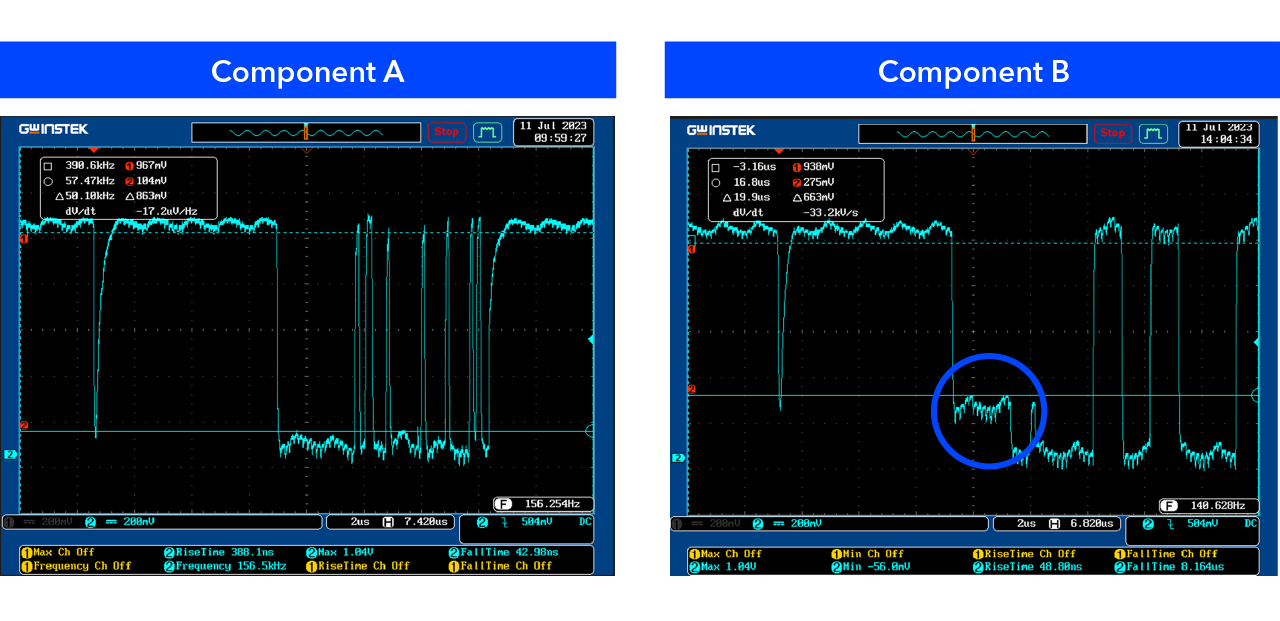

SPD Hub 訊號完整性(SI)測試:確保系統穩定運作

在高速資料傳輸環境中,傳輸線、DRAM IC、PCB 電路板等各項元素,都可能對訊號傳輸產生干擾,因此過程中的「訊號完整性(Signal Integrity, SI)」至關重要。為了確保資料準確傳輸,我們透過「示波器(Oscilloscope)」對 SPD Hub 的 I2C / I3C 訊號進行量測與分析。如下圖所示,測試結果顯示:元件 B 偶爾出現訊號振幅偏低的現象,這種不穩定可能會造成資料錯誤或不一致。

相較之下,元件 A 在時序與振幅上表現穩定,可作為維持資料傳輸可靠性與系統穩定性的參考指標。因此,選用具備穩定測試表現的 SPD Hub 元件,對於 DRAM 模組在高頻、高負載環境下的穩定運作具有決定性影響。

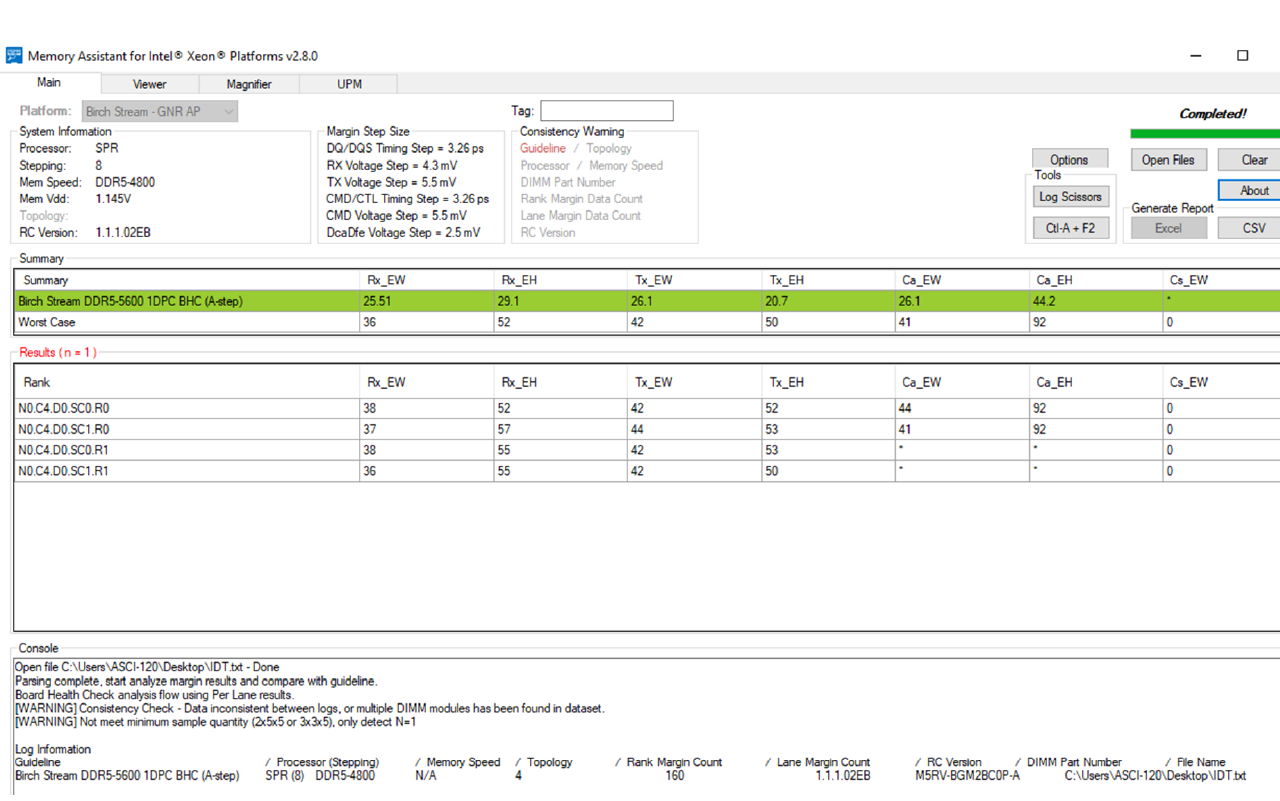

RMT 測試:驗證記憶體與主機板相容性

Intel RMT(Rank Margin Test)測試是評估記憶體與主機板之間訊號品質與相容性的業界標準方法,藉由驗證模組時序與電壓的容忍範圍,確保模組在系統平台上的穩定運作。

元件配置對訊號干擾的影響

除了測試單一零組件的訊號表現,我們也深入研究元件排列方式與 PCB 材質對訊號穩定性的影響。由於RDIMM VLP 模組的 PCB 面積縮小約 40%,因此一定程度壓縮了各項零組件之間的距離,並可能因此增加訊號干擾的風險,並影響整體訊號穩定性。

PCB 設計優化:降低干擾、提升訊號品質

為了減少訊號干擾,我們採取了兩項策略:重新設計走線方式、採用多層 PCB 結構。其中,增加 PCB 層數可降低介電常數(DK)、強化訊號穩定性。宜鼎的 DDR5 RDIMM VLP 採用高密度互連(HDI)PCB 製程,有效提升元件隔離並降低干擾風險。

透過上述完整嚴謹的驗證測試流程,我們能夠挖掘並修正各式潛在風險,並藉以打造出高品質與高效能的記憶體的 DDR5 RDIMM VLP 記憶體模組。

結語

DDR5 RDIMM VLP 記憶體模組為現今伺服器面臨的空間限制,提供了一個創新且高效的解決方案。憑藉更小的模組尺寸與優異的散熱能力,宜鼎 DDR5 RDIMM VLP 記憶體模組能讓企業在有限空間內,大幅提升記憶體容量,並在嚴謹的測試流程下,確保各式零組件組合的穩定性,展現絕佳穩定性與效能。

隨著企業對伺服器效能與擴充性的需求日益提升,DDR5 RDIMM VLP 模組正成為資料中心空間優化的關鍵利器,展現其優異的部署彈性。